# Harmonics Elimination in Multilevel Inverter with Two Unequal Voltage Batteries

Y.R. Manjunatha<sup>1</sup> M.Y. Sanavullah<sup>2</sup>

Abstract – Elimination of harmonics in a multilevel inverter with two unequal dc sources is considered. That is, for a given fundamental output voltage, our aim is to find the switching angles, that produce the fundamental while not generating specifically chosen harmonics. A procedure is given to find all sets of switching angles for which the fundamental is produced while lower order harmonics are eliminated. This is done by first converting the transcendental equations that specify the elimination of the harmonics into an equivalent set of polynomial equations. Then, using the mathematical theory of resultants, solution to this equivalent problem is found.

Keywords – Multilevel inverter, harmonics elimination, unequal voltage batteries

#### I. INTRODUCTION

Multilevel inverters provide more than two voltage levels. A desired output voltage waveform can be synthesized from the multiple voltage levels with less distortion, at low switching frequency, higher efficiency, and lower voltage rating devices. An important issue in designing an effective multilevel inverter is to ensure that, the total harmonic distortion (THD) in the output voltage waveform is small [4]. This requires an (mathematical) algorithm to determine when the switching should be done so as not to produce harmonics and a fast real-time computing system to implement the strategy. A method was reported in [2] and [3] that presented a procedure the switching angles for the H-bridges in a cascaded converter using the mathematical theory of resultants. In that work, a complete solution was presented for computing all possible switching angles that achieved the requisite fundamental voltage and eliminated lower order harmonics. However, it was assumed that the dc sources were all equal, which will probably not be the case in applications even if the sources are nominally unequal. Here, it is shown how the method in [3] can be extended to two un-equal dc source inverter. Specifically, eliminating harmonics in a multilevel converter in which the separate dc sources do not have equal voltage levels is considered. Generally each phase of a cascaded multilevel converter requires n DC sources for 2n + 1 levels. For many applications, to get many separate DC sources is difficult, and too many DC sources will require many long cables and could lead to voltage unbalance among the DC sources. To reduce the number of DC sources required when the cascaded H-bridge multilevel converter is applied to a motor drive, a scheme is proposed in [1] that allows the use of two unequal DC

sources to generate 7 level equal step multilevel inverter output instead of three equal batteries.

This scheme provides the capability to produce higher voltages (where they are needed) at low switching frequency, has inherent low switching losses and high conversion efficiency. For electric/hybrid electric vehicle motor drive applications, two H-bridges for each phase is a good tradeoff between performance and cost.

For the required fundamental output voltage, it is desired to find out the switching times (angles) that produce the fundamental and no specifically defined harmonics. In this paper, the lower order harmonics are eliminated making use of two unequal DC voltages for H-bridges.

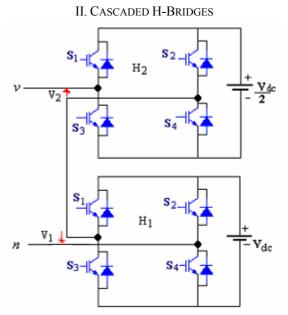

Fig. 1: Single phase multilevel cascaded H-bridge inverter.

The cascaded multilevel inverter consists of a series of H-bridge inverter units. As previously mentioned, the general purpose of this multilevel inverter is to synthesize a desired voltage from several separate dc sources (SDCSs), like batteries, fuel cells, solar cells, and ultra-capacitors. Fig. 1 shows a single-phase structure of a cascade inverter with SDCSs [6]. Each SDCS is connected to a single-phase full-bridge inverter. Each inverter level can generate three different voltage outputs,  $+V_{DC}$ , 0,  $-V_{DC}$  with different combinations of the four switches,  $S_I$ ,  $S_2$ ,  $S_3$ , and  $S_4$ .

The conventional method of generating 7 level multilevel inverter output waveform is, by using three batteries of equal magnitude and three cascaded H-bridges. In this scheme the duty cycle for each of the voltage level is

This paper first received 15 Jul 2008 and in revised form 12 Nov 2008. Digital Ref. Al70401204

<sup>&</sup>lt;sup>1</sup> Assistant Professor, Electrical Engg. Dept., U.V.C.E, K.R. Circle, Bangalore, Karnataka, India. PIN-560001. E-Mail: yrmreddygat@rediffmail.com

<sup>&</sup>lt;sup>2</sup> Prof. & Dean, EEE Dept. K.S.R. College of Technology Thiruchengode, Tamil Nadu, India

different. If this pattern of duty cycle is used on a motor drive continuously, the level 1 battery is cycled on for a much longer duration than the level 3 battery. This means that the level 1 battery will discharge much more than the level 3 battery.

To operate a cascaded multilevel inverter using two unequal DC source, we have proposed to use the first DC sources (i.e., the battery connected to first H-bridge,  $H_1$ ) as  $V_{dc}$  and the magnitude of voltage of second battery as  $\frac{V_{dc}}{2}$ . Fig. 1 shows cascaded H-bridges multilevel inverter with two unequal batteries. The DC source for the first H-bridge  $(H_1)$  is a battery or fuel cell  $V_1$  with an output voltage of  $V_{dc}$ , and the DC source for the second H-bridge  $(H_2)$  is  $V_2$  with an output voltage of  $\frac{V_{dc}}{2}$ . The output voltage of the cascaded multilevel inverter is

$$V(t) = v_1(t) + v_2(t) . (1)$$

By applying the triggering pulses to the switches of  $H_1$  appropriately, the output voltage  $V_1$  can be made equal to  $V_{dC}$ , 0, or  $-V_{dC}$ . while the output voltage of  $H_2$  i.e.,  $V_2$  can be made equal to  $\frac{V_{dc}}{2}$ , 0, or  $-\frac{V_{dc}}{2}$ . by applying the triggering pulses to the switches of  $H_2$  appropriately.

The 7 output voltages of the inverter are  $\left(\frac{V_{dc}}{2} + V_{dc}\right)$ , ...,

$$\left(\frac{V_{dc}}{2}\right)$$

, 0,  $-\left(\frac{V_{dc}}{2}\right)$ ,  $-V_{dc}$ ,  $-\left(\frac{V_{dc}}{2}+v_{dc}\right)$  which are 7

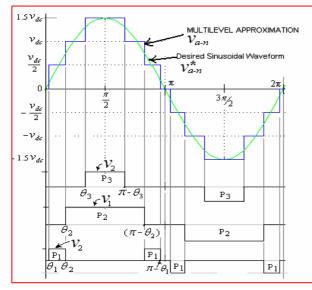

possible output levels. Fig. 2 shows the 7 level equal step output voltage waveform,

Fig. 2: Seven level equal step output voltage

This problem does not occur for the switching scheme shown above. In this paper a switching scheme is proposed in which  $v_1$ =output of  $H_1 = V_{dc}$  and  $v_2$ =output of  $H_2 = V_{dc}/2$  From  $\theta_1$  to  $\theta_2$ , voltage  $v_2$  will appear at the output (i.e.  $V_{a-n}$ ) and from  $\theta_2$  to  $\theta_3$ , voltage  $v_1$  will appear, from  $\theta_3$  to  $\theta_{\pi-\theta_3}$  voltages  $(v_1 + v_2)$  will appear, from  $\theta_{\pi-\theta_3}$  to  $\theta_{\pi-\theta_2}$  voltage  $v_1$  will appear, and from  $\theta_{\pi-\theta_2}$  to  $\theta_{\pi-\theta_1}$  voltage  $v_2$  will appear at the out put. Hence both the batteries discharge equally in every half cycle (i.e. for every 90<sup>0</sup>).

III. SWITCHING ALGORITHM FOR MULTILEVEL INVERTER

The Fourier series expansion of the 7-level equal step output voltage waveform is [4]

$$V(\omega t) = \sum_{n=1,3,5...}^{\infty} \frac{4V_{dc}}{n\pi} (\cos n\theta_1) + (\cos n\theta_2) + (\cos n\theta_3) \sin(n\omega t)$$

(2)

where 'n' is the harmonic number of the output voltage. Given a desired fundamental voltage  $V_1$ , one wants to determine the switching angles  $\theta_1$ ,  $\theta_2$ ,  $\theta_3$  so that  $V(\omega t) = V_1 \sin(\omega t)$ , and specific higher order harmonics are eliminated [8]-[10]. For three-phase motor drive applications, the triplen harmonics in each phase need not be considered as they automatically disappear in the lineto-line voltages. In this paper, the goal is to eliminate the 5th harmonic and the 7th harmonic can be filtered out. Mathematically, this can be formulated as the solution to the following equations:

$$\begin{array}{c}

\cos\theta_1 + \cos\theta_2 + \cos\theta_3 = m\\

\cos5\theta_1 + \cos5\theta_2 + \cos5\theta_3 = 0\\

\cos7\theta_1 + \cos7\theta_2 + \cos7\theta_3 = 0

\end{array}$$

(3)

This is a system of three transcendental equations with three unknowns  $\theta_1$ ,  $\theta_2$ , and  $\theta_3$ . There are many ways to solve for the angles. One approach to solving this set of nonlinear transcendental equations (3) is to use an iterative method such as the Newton-Raphson method [4]. In this work, the method given in is extended to find all solutions to (3). This methodology is based on the mathematical theory of resultants of polynomials which is a systematic procedure for finding the roots of polynomial equations. In this method, the set of equations (3) is converted to a shown polynomial system below by setting  $x_1 = \cos \theta_1$ ,  $x_2 = \cos \theta_2$ ,  $x_3 = \cos \theta_3$  and using the trigonometric identities

$$\cos 5\theta = 5\cos\theta - 20\cos^3\theta + 16\cos^5\theta$$

$\cos(7\theta) = -7\cos\theta + 56\cos^3\theta - 112\cos^5\theta + 64\cos^7\theta$

to tr

ansform (3) into the equivalent conditions

$$p_1(x) \triangleq \nabla_1 x_1 + V_2 x_2 + V_3 x_3 - m = 0$$

$$n_1(x) = \Delta \sum_{i=1}^{3} \sqrt{5x} - 20x^3 + 16x^5 = 0$$

$$p_{7}(x) \triangleq \sum_{i=1}^{3} V_{i} \left( -7x_{i} - 56x_{i}^{3} + 112x_{i}^{5} + 64x_{i}^{7} \right) = 0$$

(4)

Where  $x = (x_1, x_2, x_3)$  and  $m \underline{\Delta} V_f / (4V_{dc} / \pi)$ . The

modulation index is  $m_a = \frac{m}{n} = V_f / (n4V_{dc} / \pi)$ . This follows from the fact that each inverter has a decourse

follows from the fact that each inverter has a dc source that is nominally equal to  $V_{dc}$  so that the maximum output voltage of the multilevel inverter is  $nV_{dc}$ . Consequently, a square wave of amplitude  $nV_{dc}$  results in the maximum fundamental output possible of  $V_{f max} = 4nV_{dc}/\pi$  so that

$$m_{a}\underline{\Delta}V_{f}/V_{f\max} = V_{f}/(n4V_{dc}/\pi) = m/n$$

This is now a set of three *polynomial* equations in the three unknowns  $x_1$ ,  $x_2$ ,  $x_3$ . Further, the solutions must satisfy  $0 \le x_3 < x_2 < x_1 \le 1$  [4].

substituting

$$x_3 = \frac{\left(m - \left(V_1 x_1 + V_2 x_2\right)\right)}{V_3}$$

into  $P_5$ ,  $P_7$  leads to,

$$P_{2}(x_{1}, x_{2}) = V_{1}(5x_{1} - 20x_{1}^{3} + 16x_{1}^{5}) + V_{2}(5x_{2} - 20x_{2}^{2} + 16x_{2}^{5})$$

$$+ 5V_{3}\left(\frac{m - (V_{1}x_{1} + V_{2}x_{2})}{V_{3}}\right) - 20V_{3}\left(\frac{m - (V_{1}x_{1} + V_{2}x_{2})}{V_{3}}\right)^{3} + 16V_{3}\left(\frac{m - (V_{1}x_{1} + V_{2}x_{2})}{V_{3}}\right)^{5}$$

(5)

and

ł

$$P_{7}(x_{1},x_{2}) = V_{1}\left(-7x_{1}+56x_{1}^{3}-112x_{1}^{5}+64x_{1}^{7}\right) + V_{2}\left(-7x_{2}+56x_{2}^{3}112x_{2}^{5}+64x_{2}^{7}\right)$$

(6)

$$-7V_{3}\left(\frac{m-(V_{1}x_{1}+V_{2}x_{2})}{V_{3}}\right) + 56V_{3}\left(\frac{m-(V_{1}x_{1}+V_{2}x_{2})}{V_{3}}\right)^{3} - 112\sqrt{\frac{m-(V_{1}x_{1}+V_{2}x_{2})}{V_{3}}}\right)^{5} + 64V_{3}\left(\frac{m-(V_{1}x_{1}+V_{2}x_{2})}{V_{3}}\right)^{7}.$$

## IV. ELIMINATION USING RESULTANTS

In order to explain how one computes the zero sets of polynomial systems, utilizes *elimination theory* and uses the notion of *resultants*. Briefly, one considers  $a(x_1, x_2)$  and  $b(x_1, x_2)$  as polynomials in  $x_2$  whose coefficients are polynomials in  $x_1$  [4]. Then, for example, letting  $a(x_1, x_2)$  and  $b(x_1, x_2)$  have degrees 3 and 2, respectively in  $x_2$ , they may be written in the form

$$a(x_1, x_2) = a_3(x_1)x_2^3 + a_2(x_1)x_2^2 + a_1(x_1)x_2 + a_0(x_1)$$

(7)

$$b(x_1, x_2) = b_2(x_1)a_2^2 + b_1(x_1)x_2 + b_0(x_1)$$

(8)

The  $(n \times n)$  Sylvester matrix,

where  $n = \deg_{x_2} \{a(x_1, x_2)\} + \deg_{x_2} \{b(x_1, x_2)\} = 2 + 3 = 5$  is defined by,

$$S_{a,b}(x_1) = \begin{bmatrix} a_0(x_1) & 0 & b_0(x_1) & 0 & 0 \\ a_1(x_1) & a_0(x_1) & b_1(x_1) & b_0(x_1) & 0 \\ a_2(x_1) & a_1(x_1) & b_2(x_1) & b_1(x_1) & b_0(x_1) \\ a_3(x_1) & a_2(x_1) & 0 & b_2(x_1) & b_1(x_1) \\ 0 & a_3(x_1) & 0 & 0 & b_2(x_1) \end{bmatrix}$$

(9)

The *resultant* polynomial is then defined by,

$$r_{1}(x_{1}) = \operatorname{Res}\left(a(x_{1}, x_{2}), b(x_{1}, x_{2}), x_{2}\right) \underline{\Delta} = \det S_{a,b}(x_{1})$$

(10)

and is the result of solving  $a(x_1, x_2) = 0$  and  $b(x_1, x_2) = 0$ simultaneously for  $x_1$ , i.e., eliminating  $x_2$ . This can be referred in [12] – [15] for an explanation of this fact. The computational challenge for this approach is in the symbolic calculation of the determinant of the Sylvester matrix. However, the results in [16], [17] show that this computation can be carried out quite efficiently.

## V. EXPERIMENTAL RESULTS

To validate the proposed cascaded H-bridge multilevel motor drive control scheme, a three-phase cascaded Hbridge multilevel inverter has been developed. The switches used for this inverter are the IGBTs GT60M303 (Toshiba Make). The gating pulses are generated by microcontroller board. A 3-phase induction motor is selected with the specifications shown in the table-1 below. Also motor model is developed using MATLAB Simulink.

| S. No. | Type of the motor               | 3-∳ Induction<br>motor |  |  |

|--------|---------------------------------|------------------------|--|--|

| 1      | Rated output power              | 3700 watts (5 HP)      |  |  |

| 2      | Rated line-to-line<br>voltage   | 415 volts              |  |  |

| 3      | Rated current                   | 8.4 amps               |  |  |

| 4      | Number of poles                 | 4                      |  |  |

| 5      | Frequency of the supply voltage | 50 Hz                  |  |  |

| 6      | Rated speed                     | 1485 rpm               |  |  |

| 7      | Type of winding                 | Y-connected            |  |  |

The parameters of this motor are calculated by conducting No-load test, Blocked Rotor test and Retardation test. This motor model is simulated using MATLAB and the simulated results are compared with that of practical results. It is found that these two results are very close to each other. Then the motor model is simulated with the proposed cascaded multilevel inverter.

Table 2: Results of motor on load test, at rated voltage 415V

| S.  | $I_L$ | Win   | $T_L$ | Ν    | I/p   | O/p    | η    |

|-----|-------|-------|-------|------|-------|--------|------|

| No. | Amps  | Watts | N-m   | rpm  | Watts | Watts  | %    |

| 1   | 4.5   | 200   | 0     | 1480 | 200   | 0      | 0    |

| 2   | 4.9   | 900   | 2.53  | 1463 | 900   | 387.6  | 43   |

| 3   | 5.5   | 1600  | 7.6   | 1413 | 1600  | 1124.5 | 70.2 |

| 4   | 6.1   | 2100  | 10.96 | 1376 | 2100  | 1579   | 75.2 |

| 5   | 6.8   | 3100  | 15.18 | 1320 | 3100  | 2098   | 67.6 |

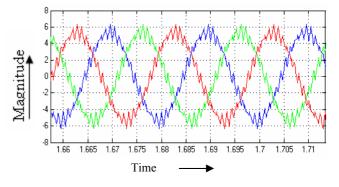

Fig. 3: Stator current, motor fed from SPWM Inverter

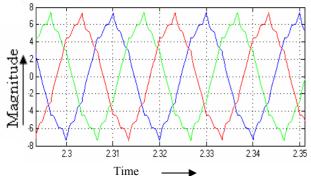

Fig. 3 shows the stator currents of three phase induction motor on no-load fed from 2 level inverter. In this fig. even though the waveform looks close to sinusoidal, it has distortion. Fig. 4 is the stator currents of the same motor fed with 7 level inverter. Fig 5 shows the spectrum. It is

Table 1: Specifications of the motor

observed that the distortion is almost reduced. Hence the motor runs smoothly and safely. Fig. 6 is the three phase output voltage of multilevel (7 Level) inverter with two unequal voltages.

Fig.4: Stator current, motor fed from ML Inverter

1.6 1.4 1.2 1 0.8 Magnitude 0.6 0.4 0.2 0 -0.2 З Ļ 5 Б П 9 Harmonic number Fig. 5: Harmonic spectrum of Line-to-Line Vg 400 300 200 Magnitude 100 0 100 200 30 0.09 0.0 0.08 Time in Sec.

Fig. 6: Output voltage waveform of MLI (3 phase)

## IV. CONCLUSION

Elimination theory and the notion of resultants can be used to eliminate the lower order harmonics in a multilevel inverter that has unequal dc sources. This method is expected to have widespread application as most multilevel converters do not have dc sources that are equal. Also as the number of batteries are reduced, the Electrical Vehicle mileage will also be improved. Both the batteries discharge equally in every half cycle (i.e. for every 90<sup>°</sup>). By looking into harmonic spectrum, we observe that, all the lower order harmonics are eliminated, only the magnitude of 7<sup>th</sup> harmonic, whose frequency is very high (350Hz) compared to fundamental frequency (50Hz). Hence it can be easily filtered out using a filter capacitor.

Fig. 7: Photograph of experimental setup

#### References

- Y.R. Manjunatha, M.Y. Sanavullah, "Generation of equal step multilevel inverter output using two unequal batteries", International journal of electrical and power engineering. Vol. 1, Issue 2, 2007, pp. 206-209.

- [2] J. Chiasson, L. M. Tolbert, K. McKenzie, and Z. Du, "A complete solution to the harmonic elimination problem", IEEE Trans. Power Electron., Vol. 19, No. 2, Mar. 2004, pp. 491–499.

- [3] John N. Chiasson, L.M. Tolbert, Keith J. McKenzie, Zhong Du, "Control of a multilevel converter using resultant theory", IEEE Trans. Contr. Syst. Technol., Vol. 11, No. 3, May 2003, pp. 345–354.

- [4] Leon .M Tolbert, John N. Chiasson, Zhong Du, Keith J. McKenzie. "Elimination of harmonics in a multilevel converter with nonequal DC sources", IEEE Trans. Ind. Appl., Vol. 41, No. 1, January / February 2005 pp. 75-82.

- [5] Leon .M Tolbert, Fang Zheng Peng and Thomas G. Habetler, "Multilevel converter for large electric driver", IEEE Trans. Ind. Appl., Vol. 35, No.1, January/February, 1999, pp. 36-44.

- [6] J. S. Lai and F. Z. Peng, "Multilevel converters—a new breed of power converters", IEEE Trans. Ind. Appl., Vol. 32, No. 3, , May/Jun. 1996, pp. 509–517.

- [7] Zhong Du, Leon M. Tolbert, John N. Chiasson, Burak Ozpinec Hui Li, Alex Q. Huang, "Hybrid Cascaded H-bridges Multilevel Motor Drive Control for Electric Vehicles", proceedings of PESC 07, June 2007.

- [8] H. S. Patel and R. G. Hoft, "Generalized harmonic elimination and voltage control in thyristor inverters: Part I harmonic elimination", IEEE Trans. Ind. Appl., Vol. 9, May / June 1973, pp. 310-317.

- [9] H. S. Patel and R. G. Hoft, "Generalized harmonic elimination and voltage control in thyristor inverters: Part II -voltage control technique", IEEE Trans. Ind. Appl., Vol. 10, Sept./Oct. 1974, pp. 666-673.

- [10] P. N. Enjeti, P. D. Ziogas, J. F. Lindsay, "Programmed PWM techniques to eliminate harmonics: A critical evaluation", IEEE Trans. Ind. Appl., Vol. 26, No. 2, March/April. 1990, pp. 302 - 316.

- [11] Leon. M Tolbert, John Chiasson, Zhong Du, Keith McKenzie. "Elimination of harmonics in a multilevel converter for HEV applications", IEEE, 2002, pp.135-142.

- [12] T. Kailath, Linear Systems. (Englewood Cliffs, NJ: Prentice-Hall, 1980).

- [13] D. Cox, J. Little and D. O'Shea, Ideals, Varieties, and Algorithms: An Introduction to Computational Algebraic Geometry and Commutative Algebra, 2nd ed. (Berlin, Germany: Springer-Verlag, 1996).

- [14] J. von zur Gathen and J. Gerhard, Modern Computer Algebra. (Cambridge, U.K. Cambridge Univ. Press, 1999).

- [15] C. Chen, Linear Systems Theory and Design, 3rd ed. (London, U.K. Oxford Univ. Press, 1999).

- [16] M. Hromcik and M. 'Sebek, "Newalgorithm for polynomial matrix determinant based on FFT," in Proc. Eur. Conf. Control, ECC'99, Karlsruhe, Germany, Aug. 1999, CD-ROM.

- [17] M. Hromcik and M. Sebek, "Numerical and symbolic computation of polynomial matrix determinant", in Proc. of Conf. Decision and Control, Tampa, FL, Vol. 2, 1999, pp. 1887–1888.

#### BIOGRAPHIES

Y.R. Manjunatha. Member IEEE, Life member ISTE, Received the B.E. degrees in Electrical & Electronics Engineering from University of Mysore and M. Tech. degree in electronics from Power Vishwaraya University, Technological Belgaum. Karnataka, India. He is pursuing the Ph.D. degree. His research interests are "multilevel inverters". He is currently working as an Assistant Professor in the department of Electrical Engineering, University college Visveswaraya Engg. University, Bangalore K.R. Circle,

Bangalore, India.

**M. Y. Sanavullah** received the B.E. degrees in Electrical Engineering & M.Sc. (Engg.) both from Madras University and Ph. D from Anna University, has 38 years of teaching experience. He has 27 publications in both national & international conference and journals. Presently working as Professor and Dean, Electrical Engg. K.S.Rangasamy College of Technology, Tamilnadu, India.